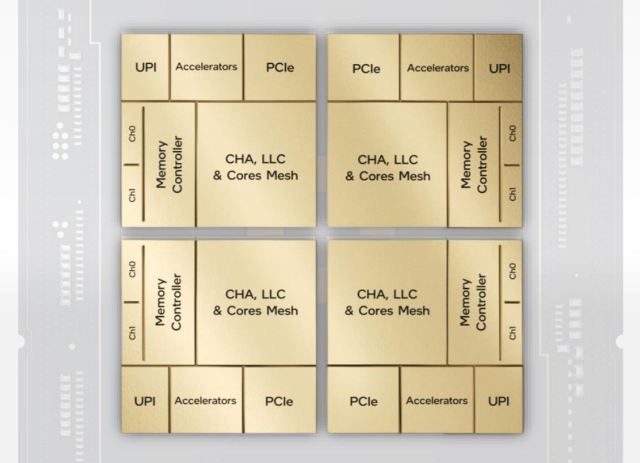

Intel Corp.’un Sapphire Rapids kod adlı dördüncü nesil Xeon işlemcisi, şirket, Mimarlık Günü etkinliği sırasında açıkladığı dört yongadan oluşuyor.

Bu, Intel’in daha önce teknolojiyi geçen yıl Stratix 10 FPGA hattına ekleyen Xeon veri merkezi CPU hattına ilk kez yongaları entegre ettiği anlamına geliyor . Stratix 10, kalıpları bağlamak için bir silikon aracı kullanan Intel’in gelişmiş paketleme teknolojisi olan gömülü çoklu kalıp ara bağlantısını (EMIB) birleştiren ilk üründü . Daha önce Intel, EMIB kullanmayan Kaby Lake-G adlı bir üründe CPU’larını bir AMD GPU ile birleştirdi. Intel ayrıca Foveros (Lakefield hattında kullanılan) adlı dikey kalıp istifleme teknolojisi geliştirdi, ancak bu hafta Sapphire Rapids’de kullanılmayacağını doğruladı.

Intel’in Sapphire Rapids baş mühendisi Nevine Nassif, EE Times ile Mimarlık Günü öncesi röportajında , yonga stratejisinin arkasındaki itici güç olarak EMIB tarafından sağlanan maliyet ve verim avantajlarını belirtti.

Nassif, “Buna uzun zaman önce, 15-16 yıl önce bakmaya başladık, ancak o zaman sahip olmadığımız şey EMIB teknolojisiydi” dedi. “Geçmişte, bir tasarımı iki kalıba ayırmayı denediğimizde, [ara bağlantı] için ihtiyaç duyduğunuz üst alan çok büyüktü – bu kalıplar arasındaki güç çok büyüktü ve gecikmeler performansı öldürürdü.”

EMIB, Intel’in 55 mikronluk çarpma aralığına kadar ölçeklenmesini sağladı; bu, kalıplar arası ara bağlantı ekleme ek yükünün yeterince azaldığı ve gecikmenin yönetilebilir seviyelere indirildiği anlamına geliyor.

Sapphire Rapids’in yonga geliştirmesi, Intel mühendisleri bir kalıbı ikiye veya dörde bölmeye çalıştığında başladı. Amaç, özellikle prototip aşamasında proses teknolojisi tarafından üretilen verimler göz önüne alındığında, prototip silikonun kullanılabilirliğini hızlandırmaktı (Sapphire Rapids, Intel’in 7 nm proses teknolojisi üzerine inşa edilmiştir ).

Sapphire Rapids’in öncülü Ice Lake’i geciktiren önceki süreç düğümünde sorunlarla karşılaşıldığında , chiplet yaklaşımı cazip bir seçenek olarak ortaya çıktı.

Nassif, “Süreçte daha sonra, daha yekpare bir şeye geri dönmek istedik… [ancak] zaman geçtikçe ve işler ertelendikçe, rekabetçi kalabilmek için daha fazla çekirdek istedik, ” diye açıkladı Nassif. Chiplet’ler “dürbün sınırlarının ötesine geçmenin iyi bir yolu olarak ortaya çıktı. İstediğimiz çekirdek sayısına sığdırmak için kalıbı en az ikiye bölmemiz gerekti.”

Modüler kalıp kumaş

Kalıbı bağlamak için kullanılan teknolojiye, ağın bant genişliğini kalıplar arasında taşıyan modüler kalıp kumaşı (MDF) denir. Dördü de, tasarımın monolitik özelliklerini koruyan bir ağ ile birbirine bağlanmıştır. Herhangi bir çekirdek, dört kalıptan herhangi birinde bulunan diğer çekirdeklerle konuşabilir ve paylaşılan önbelleğe dört kadranın tamamında ve ayrıca dört kadranda G/Ç’ye erişebilir.

Nassif, “Bir çekirdek kendi çeyreğiyle sınırlı değil, ancak elbette daha iyi performans görecek, çünkü her şey yakında, ancak her çekirdek için her şey mevcut” dedi. “Her zaman UPI [Intel Ultra-Path Interconnect] üzerinden geçen iki ve dört soket sistemimiz var, böylece UPI aracılığıyla diğer soketteki bir çekirdekle konuşabiliyoruz.”

Stratix 10 ile, EMIB heterojen kalıbı birleştirmek için kullanıldı (bir FPGA kalıbı artı 4 alıcı-verici kalıbı artı iki HBM yongası). Basit olması için, dört Sapphire Rapids kalıbı, aynalı çiftler dışında aynıdır.

Nassif, “Bu, bu tür şeylere ilk girişimiz olduğundan, daha basit bir şeyle gittik – basit değildi – ama daha basit,” dedi. “Tasarım açısından bakıldığında, bunlar aynıdır, bu yüzden sadece çalışan bir kalıbı doğrulamak zorunda kaldık ve ardından kalıptan kalıba giden arayüzleri doğrulamak zorunda kaldık. Ondan sonra, bunun işe yarayabileceğinden oldukça emindik.”

Gelecek nesil veri merkezi CPU’ları pakette heterojen kalıplar kullanabilir, ancak Sapphire Rapids kullanamaz.

Geliştirme zorlukları

Nassif, mümkün olduğu kadar monolitik bir kalıp gibi görünen dört kalıplı bir tasarımın sürdürülmesinin bazı geliştirme sorunlarına neden olduğunu kabul etti.

İdeal olarak Intel, gerekli silikon alanını azaltmak için kalıplar arasında saat hızını dört kat artırmak istedi, ancak bit-hata oranı çok yüksekti. Ayrıca, yapılandırma gecikmeyi artıracak düzeltme devresine ihtiyaç duyacaktı. Ağ hızında gönderme, çok fazla alan yükü ile çok tutucuydu.

“Gecikmeye olan etkiyi en aza indirmenin, alan yükünü en aza indirmenin, ek yükü en aza indirmenin ve ölümden ölüme kadar hata yapmadığımızdan emin olmanın bir yolunu bulmamız gerekiyordu” dedi. “Tatlı noktayı bulmamız gerekiyordu.”

Sinyal bütünlüğünü korurken güç tüketimini azaltmak için kalıptan kalıba iletişim için voltajın da optimize edilmesi gerekiyordu.

Ağ bant genişliğini desteklemek için kalıplar arasındaki veri bant genişliğinin de korunması gerekiyordu. Tasarımcılar, bant genişliğine karşı güç tüketimini optimize etmek için farklı iş yüklerindeki veri modellerine baktı.

Nassif, “Bir ton güç yakmamak için verileri nasıl göndereceğimiz konusunda akıllıca şeyler yapmaya çalıştık” dedi. “Ayrıca, belirli durumlarda geri çekileceğimizden veya diğer durumlarda daha fazla zorlayacağımızdan emin olmak için, verileri gönderirken gereksiz güç yakmadığımızdan emin olmak için geçerken verileri izledik.”

Belirli iş yükleri için optimize edilmiş farklı veri aktarım modları, Sky Lake’ten (2015) beri kullanılmaktadır. Sapphire Rapids’in kullanıma hazır veri aktarım modu, Dörtlü modu (bir kalıpla sınırlı trafik) kullanır, ancak müşteriler, güç tüketimi pahasına diğer modlara geçmeyi seçebilir.

chiplet geleceği

Nassif, Sapphire Rapids CPU’ların yalnızca dört yongaya sahip olacağını doğrularken, gelecek nesiller daha fazlasına sahip olabilir.

“Bizi dört ölümle sınırlayan hiçbir şey yok ve farklı zamanlarda Sapphire Rapids üzerinde çalıştığımız için dört, altı veya sekiz olarak düşündük” dedi. “Teknolojinin kendisinde bizi dörde sınırlayan hiçbir şey yok. Daha çok elimizdekilerle ve ilk nesil için almak istediğimiz riskle ilgiliydi.”

Aynı kalıpta olmanın performans avantajlarını, nişangah sınırlamaları ve verim ile dengelemeye gelir. Tatlı nokta, kabaca 400 mm 2 boyutlu bir kalıpta görünüyor.

Sapphire Rapids kalıplarının bağlantı şekli göz önüne alındığında, gerçekten sadece dört kalıp olabilir.

Nassif, “İşleri modüler hale getirmenin yollarını arıyoruz, bu yüzden belirli ürünler için yalnızca iki kalıpla çalışabilirim, ardından çekirdekleri veya G/Ç’leri artırmak istediğimde belki başka bir kalıp ekleyebilirim” dedi. Kalıbı nasıl karıştırdığınız ve eşleştirdiğiniz konusunda işleri daha modüler hale getirmek istiyoruz. Bu [şimdiki] nesilde sahip olacağımız bir şey değil, gelecek için baktığımız bir şey.”

Bellek ve G/Ç

DDR5 desteği de Sapphire Rapids ile yenidir ve bellek frekanslarını Ice Lake’den daha yükseğe taşır. En yeni Xeon işlemci, her kalıpta toplam sekiz kanalı destekleyen bir DDR5 bellek denetleyicisine sahiptir.

Gelecek sürümler, dört yüksek bant genişliği belleği (HBM) yığınını destekleyecektir. Bu yinelemeler, EMIB aracılığıyla HBM belleğine bağlanan her kalıpta bir HBM denetleyicisi gerektirecektir. Bu sürümlerde, CPU kalıpları yalnızca DDR5 sürümlerinden biraz farklı olacaktır; HBM denetleyicisine yer açmak için kriptografi, sıkıştırma ve diğer görevler için bazı hızlandırıcılar kaldırılacak (ancak CPU çekirdeğini kullanmadan bellek ve G/Ç arasında veri hareketine yardımcı olan yeni veri akışı hızlandırıcısı DSA korunacak ). Nassif, HBM bant genişliğini destekleyen ağda da bazı değişiklikler olduğunu söyledi. HBM-etkinleştirilmiş Sapphire Rapids kalıbı DDR5 denetleyicilerini koruyacak, böylece DDR5 ve HBM birlikte kullanılabilir.

Ice Lake’in gecikmesi, Intel’in daha fazla PICe hattıyla birlikte Sapphire Rapids’de PCIe Gen5’i tanıtmasına yol açtı. Şeritler, sırayla tutarlı bellek işlemlerini destekleyen yeni hesaplama ekspres bağlantı (CXL) protokolünü destekler. CXL ayrıca veri merkezlerinde hızlandırıcı ve bellek genişletme için kullanılır. Nassif bunların gelecekteki ürünlerde olacağını söylese de, PCIe hatları çatallanabilirken, mevcut nesil CXL hatları yapılamaz.

Altın Koy çekirdeği

Sapphire Rapids CPU’lar, Intel’in yeni Golden Cove çekirdek mimarisini, özellikle performans için optimize edilmiş P-çekirdekli sürümünü kullanacak. Alder Lake gibi istemci tarafı işlemciler, güç verimliliği için optimize edilmiş bir sürüm olan hem P hem de E çekirdeklerini kullanacak. Geleceğin Sapphire Rapids işlemcileri E-çekirdek kullanmayacak, ancak gelecek nesil Xeon kullanabilir.

Golden Cove çekirdeği, Intel’in yeni nesil AI hızlandırma teknolojisi olan DLBoost’u içerir. Bu sürümde, yonga üreticisi, AI iş yüklerinde yaygın bir matematiksel işlem olan matris çarpma için talimatlar ekledi. AMX (gelişmiş matris uzantıları) olarak adlandırılan yeni talimatlar, daha önce DLBoost’a eklenen gelişmiş vektör uzantıları (AVX-512) talimatlarına ektir .

AMX mimarisinde iki bileşen vardır:

- Fayanslar, her biri 1 Kb boyutunda 8x iki boyutlu kayıtlardan oluşan yeni bir durum bileşeni. Kayıt dosyası, yükle/sakla ve temizle gibi temel veri operatörlerini destekler. Karolar üzerinde çalışan yardımcı işlemciler tarafından daha karmaşık işlemler gerçekleştirilir. Kutucuk durumu, XSAVE mimarisinde yeni uzantılar gerektiren işletim sistemi tarafından yönetilir.

- İkinci bileşen TMUL’dir (karo matrisi çarpımı) ve karolara eklenen ilk yardımcı işlemci olarak faturalandırılır. Sistolik dizi, 32 bit birikimli INT8 ve tek duyarlıklı birikimli BFloat16 lezzetlerini destekler.

Intel’in matris çarpma mikro karşılaştırmaları, AMX ile hızlandırmanın tek başına AVX-512 vektör sinir ağı talimatlarını kullanmaktan 7,8 kat daha hızlı olduğunu gösterdi. Sapphire Rapids’in mevcut uygulamasındaki AMX tepe hesaplama verimi, çekirdek başına döngü başına 2000 INT8 işlemi (AVX-512’den 8 kat daha yüksek) veya çekirdek başına döngü başına 1.000 BFloat16 işlemidir.